在3G网络的助力下,高清移动数字化监控系统得以实现。本文将介绍一种集视频采集、数据压缩、联动报警、卫星定位及网络传输于一体的3G移动视频监控系统。这种系统在实时性和视频质量上面临两大挑战:首先是H.264压缩算法的耗时问题,这在资源受限的嵌入式环境中尤其显著。然而,随着达芬奇技术的成熟,其ARM 926EJ-S和DSP C64x+的双核架构,使得H.264压缩算法得以在DSP的Codec Server端独立运行,从而确保了系统的实时性。

其次,3G无线网络传输的视频质量和实时性也是一个关键问题。为了解决这一问题,我们可以从两个方面着手:一是缩短视频数据的传输时间,通过使用最高效的H.264编码技术减少传输的信息量,并动态自适应调整视频数据的帧码率以适应无线带宽的变化;二是实现视频数据传输的QoS机制,通过实时传输控制协议RTCP和实时传输协议RTP的配合使用,以有效的反馈和最小的开销实现传输效率最佳化。

接下来,我们来看看系统的架构和工作原理。本系统采用达芬奇处理器(TMS320DM6446)、DDR2 SDRAM(MT47H64M16)、NAND FLASH(K9F1208X0C)、视频解码器TVP5150、3G芯片(中兴MC8360)、GPS卫星定位芯片以及外围接口芯片的方案。CCD摄像机采集的模拟视频信号,经过视频解码器进行模/数转换,输出数字视频信号,再经过预处理和编码,通过USB 2.0总线送入3G传输芯片,最终无线传输到远程视频监控中心。

在硬件方案设计方面,视频采集与解码设计采用了TI公司的视频解码芯片TVP5150,该芯片支持多种视频格式,并能输出8位4:2:2的ITU BT.656信号。DDR2 SDRAM内存接口设计则选择了Micron公司的MT47H64M16BT型号DDR2芯片,通过两片16位芯片组成32位数据总线,形成256MB的内存系统。

电源设计采用了TI公司的TPS75003和TPS62040电源管理芯片,分别提供+5V、+3.3V、+1.8V和+1.2V四种电源,确保系统的稳定运行。

总之,这种3G移动视频监控系统通过先进的技术和设计,解决了实时性和视频质量的问题,为数字化视频监控系统的发展提供了有力支持。随着技术的不断进步,我们有理由相信,这一系统将在更多领域发挥重要作用,为社会的安全和便捷贡献力量。

0 引言

在数字化视频监控技术飞速发展的今天,数字化视频监控系统正迅速的深入到各行业,如企业、煤矿、学校、公共场所,为人们的工作和生活带来了一次大变革。由于能够在达芬奇平台中实现数字视频、音频、语音与话音技术,因此达芬奇技术可以为数字化视频监控系统的当前变革打下基础。

与此同时,随着3G 网络的开通,更为高清移动数字化监控系统提供了实现的可能。

本文中要设计的3G移动视频监控系统是一种能提供视频采集、视频数据压缩、联动报警、卫星定位及网络传输功能于一体的一种移动实时视频监控系统。其主要技术瓶颈就在于:①其系统耗时是否能保证其实时性要求,关键为H.264压缩算法耗时。由于嵌入式环境资源的限制,在视频数据的实时性传输和图像质量方面,尤其是多路的情况下,其一直都得不到保证。但是随着达芬奇技术的成熟,其ARM 926EJ-S与DSP C64x+ 的双核架构,H.264 压缩算法独立运行在DSP的 Codec Server 端,解决了系统耗时保证其实时性要求。②其3G 无线网络传输能否保证视频质量及实时性。在保证视频质量及传输实时性要求上,可以从两个方面入手:①缩短视频数据的传输时间,使用当前最高效的H.264 编码技术缩小传输的信息量,采用动态自适应调整视频数据的帧码率来减少传输的信息量,以适应无线带宽及抖动。②实现视频数据传输的QoS 机制,自己设计实现了3G 无线传输的QoS 机制,选用实时传输控制协议RTCP 和RTP 配合使用,能以有效的反馈和最小的开销实现传输效率最佳化,因此保证了视频质量及其实时性。

1 系统架构及工作原理

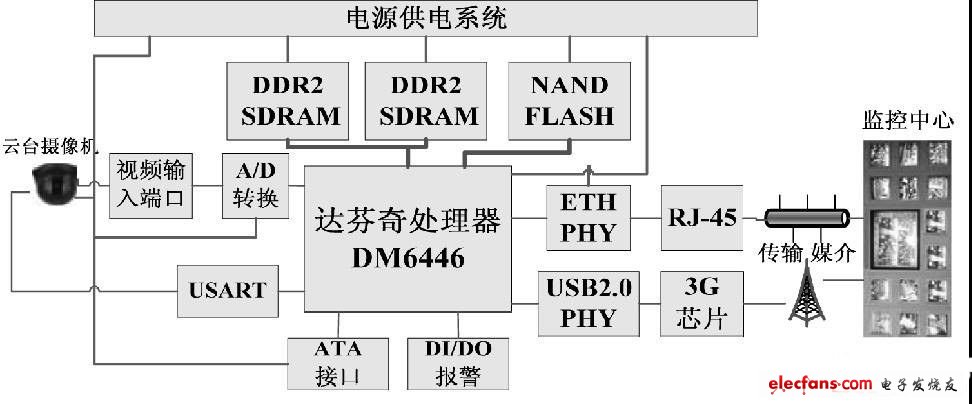

本系统采用的是由达芬奇处理器(TMS320DM6446)、DDR2SDRAM(MT47H64M16)、NAND FLASH(K9F1208X0C)、视频解码器TVP5150、3G 芯片(中兴MC8360)、GPS 卫星定位芯片加上外围接口芯片的方案。CCD 摄像机采集模拟视频信号传入视频解码器内,进行模/ 数转换, 输出符合ITU-BT.656标准的数字视频信号,然后将数字视频信号传到视频处理子系统的前端进行预处理,将数字视频信号通过本人设计的OSD字幕添加算法加入白底黑边字幕后,经过Codec Engine 编码后通过USB2.0 总线端口送入3G 传输芯片,无线传输到远程视频监控中心;达芬奇处理器检测进行卫星定位命令,通过串口接收GPS 卫星定位信息,然后将GPS 卫星定位信息传入到3G 传输芯片,无线传输到远程视频监控中心,在地图上标定其坐标点及其移动轨迹。DM6446 上的DSP 端主要负责视频编解码工作,ARM 端做为控制视频解码芯片、3G 传输芯片、GPS 定位芯片和外围接口芯片的控制器。系统硬件结构框图如图1 所示。

图1 系统硬件结构框图

2 硬件方案设计

2.1 视频采集与解码设计

本设计中选用TI 公司的视频解码芯片TVP5150 完成视频图像的模/ 数转换。TVP5150 是超低功耗、支持NTSC/PAL/S E C A M 等格式的高性能视频解码器,它正常工作时功耗仅115mW,并具有32 脚TQFP 超小封装。它可以接收两路CVBS或一路S-Video 信号,通过I2C 总线设置其内部寄存器,可以输出8位4:2:2的ITU BT.656信号。

TVP5150 芯片采用14.31818 MHz 晶振做为输入时钟,数字和模拟输入电压为1.8V,IO 口电压为3.3V;信号输入有AIP1A 和AIP1B 两路,并且都进行阻抗匹配设计,防止对输入信号的反射;YOUT[0:7]输出8 路YcbCr 信号,行场同步信号选择引脚HSYNC 和VSYNC 输出;SCLK 引脚向DM6446 芯片输出27MHz 时钟信号,用来同步数据采集。

2.2 DDR2 SDRAM 内存接口设计

内存主要用来缓存视频输入图像数据,存储ARM 和DSP代码等。DDR2 内存是一种新型高速、大容量的双速率同步存储器,相对于DDR,DDR2 具有更高的频宽、更低的功耗、更好的高速效能。

本设计选用Micron 公司的MT47H64M16BT 型号DDR2芯片,该芯片单片容量为1Gb,提供16 位字长数据总线接口,芯片采用1.8V 做为输入电压,其内存支持差分锁存信号,可以保证电路在高速情况下准确的锁存总线上的数据,使系统更加稳定可靠。为提高系统内存容量并最大限度利用DDR2控制器的32 数据总线,设计选用两片MT47H64M16BT,分别作为数据总线的高低16 位,组成32 位数据总线、大小为256Mbyte 的内存系统。将两片16 位DDR2 芯片与32 位总线的DDR2 控制器连接时,把数据总线和相应的数据选通信号及字节使能信号与相应DDR2 芯片分别连接,其它信号两片DDR2 芯片公用。此时,32 位数据总线的DDR2 控制器可同时访问两片DDR2 芯片。

2.3 电源设计

本设计选用TI 公司的TPS75003 和TPS62040 电源管理芯片,T P S 7 5 0 0 3 具有两路最大提供3 A 的拓扑电源和一路300mA LDO 电源,每个Buck 输出电压范围在1.2V 至6.5V 之间,LDO 输出电压范围在0.9V 至6.5V 之间,输入电压范围在2.2V 至6.5V 之间。TPS62040 是高效异步开关DC/DC 转换电源,其转换效率达到95%,输入电压范围在2.5V 至6.0V,输出电压在0.7V 至6.0V,因此都可通过主电源+5V 供电。

系统电源分为+5V、+3.3V、+1.8V、+1.2V 四种,系统主供电电源为+5V,其余均由+5V 电源供给。因此,采用一片TPS75003 和一片TPS62040 完成系统四种电源的转换。设计用TPS75003 的SW1 引脚经过SI2323 续流整形后输出1.2V 电压用于DM6446 内核供电,IS1 引脚连接参考电压,FB1 引脚接输出1.2V 电压作为反馈,SW2 引脚输出3.3V 电压用于DM6446 外设接口供电。TPS62040 的SW1 和SW2 引脚短接后输出1.8V 电压用于DM6446 存储器接口供电,FB 引脚连接1.8V 作为反馈输入。这样,用一片TPS75003 和TPS62040 电源管理芯片就可以满足本系统供电。TPS75003 和TPS62040电源转换电路如图2 所示。

图2 TPS75003 和TPS62040 电源转换电路图