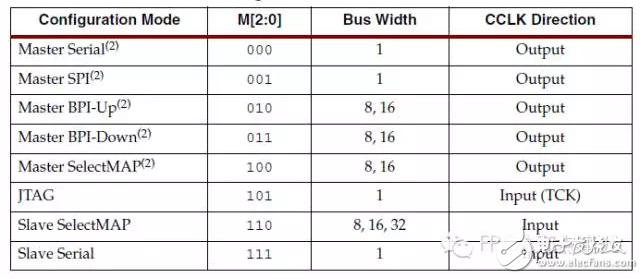

首先,让我们了解一下硬件连接。在Slave SelectMAP模式下,M[2:0]应设置为110,这表示总线宽度可以是8、16或32位。本文将聚焦于32位模式的配置和回读。

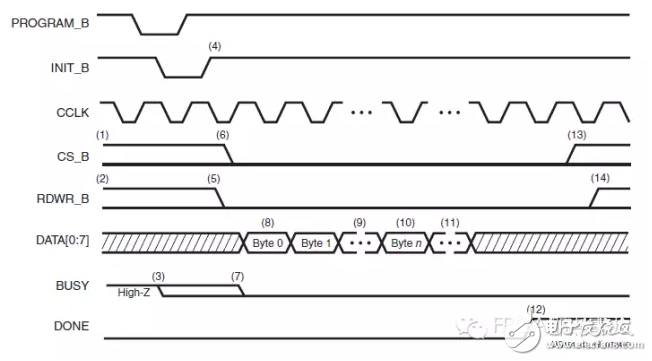

配置过程实际上是将mcs文件中的配置字序列通过SelectMAP接口写入FPGA。配置字的写入时序如图所示,其中包括了PROGRAM_B、INIT_B、CCLK、CS_B、DATA[7:0]、RDWR_B、BUSY以及DONE等信号。其中,DATA接口是双向的,而PROGRAM_B、INIT_B、CCLK、CS_B、RDWR_B是DUT的输入,由配置FPGA产生。CCLK的频率通常为25MHz。BUSY和DONE是DUT的输出,配置FPGA通过这两个信号来判断DUT是否配置完成。

配置字序列及其具体含义如下:首先是 Dummy Word(无效字),用于初始化;接着是BusWidthWord(总线宽度字),用于指定数据总线宽度;然后是Sync Word(同步字),用于同步配置过程。

在Slave SelectMAP模式下,默认的数据总线宽度为8位。DATA[7:0]首先检测总线宽度序列,如果检测到0xBB后是0x11,则总线宽度为8位;如果是0x22,则总线宽度为16位;如果是0x44,则总线宽度为32位。总线宽度序列检测完毕后,接收同步字序列AA995566。

接下来,按照特定顺序发送状态寄存器等写指令,对FAR(功能地址寄存器)、CMD(命令寄存器)等状态寄存器进行写操作,使FPGA处于待接收配置字状态。这些指令包括NOOP(无操作)、write(写操作)等,通过这些操作,FPGA可以接收并解析配置数据。

配置完成后,需要进行回读以验证配置的正确性。回读过程与配置过程类似,但方向相反。通过读取DUT的状态寄存器和配置数据,可以确认配置是否成功。

在配置过程中,还需要考虑一些关键的状态寄存器。例如,COR0和COR1寄存器用于配置FPGA的运行模式,ID寄存器用于识别FPGA型号,MASK和MASKR寄存器用于控制配置数据的写入。

此外,FPGA配置bit流包含两种类型的配置字指令。第一种类型为读写操作指令,用于短字节的写操作;第二种类型必须跟随在类型一之后,用于长字节的写操作。

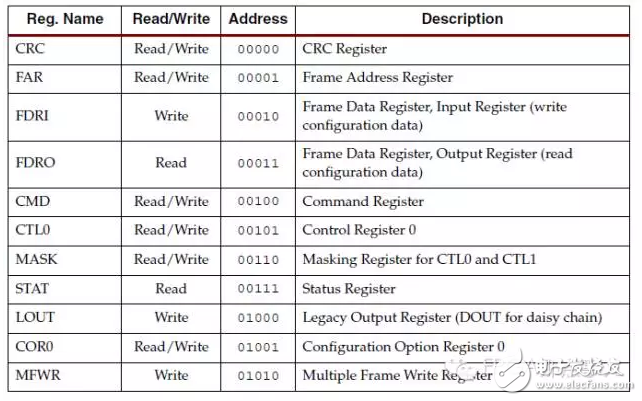

最后,一些状态寄存器的地址如下所示,这些地址在配置过程中至关重要,它们帮助配置FPGA并确保其正常运行。

通过以上介绍,我们了解了如何通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA。这一过程虽然复杂,但通过合理的设计和仔细的操作,可以确保FPGA的正常工作和性能优化。

通过SELECTMAP32接口配置和回读XILINX公司生产的V5系列SRAM型FPGA,被配置的FPGA以下简称DUT,产生配置时序的FPGA简称配置FPGA。

上图描述了FPGA主动配置和从配置多种模式下M[2:0]及时钟CCLK的状态。

首先硬件上应将M[2:0]接成110,即Slave SelectMAP模式,该模式下总线宽度分8,16,32bit三种,本文按照32bit模式配置和回读。

1.配置

配置的过程就是将mcs文件中的配置字序列通过SelectMAP接口写入FPGA,配置字的写时序如下图:

如上图所示,SelectMAP接口包含PROGRAM_B、 INIT_B、CCLK、CS_B、DATA[7:0](8bit模式)、RDWR_B、BUSY以及DONE。其中DATA接口为双向,PROGRAM_B、 INIT_B、CCLK、CS_B、RDWR_B为DUT的输入,由配置FPGA产生,CCLK频率为25MHz。BUSY和DONE为DUT的输出,配置FPGA根据BUSY和DONE信号判断DUT是否配置完成。

mcs中配置字序列以及具体含义如下:

FFFFFFFF Dummy Word

000000BB BusWidthWord

11220044 8/16/32BusWidth

FFFFFFFF Dummy Word

FFFFFFFF Dummy Word

AA995566 Sync Word

以上为总线宽度检测和同步字序列。在SlaveSelectMAP模式下,默认配置数据总线宽度为8bit,DATA[7:0]首先检测总线宽度序列,如果DATA[7:0]检测到0xBB后是0x11,则总线宽度为8bit,如果0xBB后是0x22,则总线宽度为16bit,如果0xBB后是0x44,则总线宽度为32bit,在总线宽度序列检测完毕后,接收同步字序列AA995566。

在发送完同步字后,按照以下顺序发送状态寄存器等写指令,对FAR、CMD等状态寄存器进行写操作,使FPGA处于待接收配置字状态。

20000000 Type 1NOOP

30020001 Type 1 write1 words to WBSTAR

00000000 Warm BootStart Address

30008001 Type 1 write1 words to CMD

00000000 NULL

20000000 Type 1NOOP

30008001 Type 1 write1 words to CMD

00000007 RCRC

20000000 Type 1NOOP

20000000 Type 1NOOP

30022001 Type 1 write1 words to TIMER

00000000 TIMERvalue

30026001

00000000

30012001 Type 1 write1 words to COR0

02003F35 done@4 m@0l@0 gts@3 gwe@5

3001C001 Type 1 write1 words to COR1

00000000 COR1value

30018001 Type 1 write1 words to ID

03300093 ID code

30008001 Type 1 write1 words to CMD

00000009 Switch

20000000 Type 1NOOP

3000C001 Type 1 write1 words to MASK

00400000 MASKvalue

3000A001 Type 1 write1 words to CTL0

00400000 CTL0value

3000C001 Type 1 write1 words to MASKR

00000000 MASKvalue

30030001 Type 1 write1 words to CTL1

00000000 CTL1value

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

20000000 Type 1NOOP

30002001 Type 1 write1 words to FAR

00000000 FARvalue

30008001 Type 1 write1 words to CMD

00000001 WCFG

20000000 Type 1NOOP

30004000 Type 1 write0 words to FDRI

50177910 Type 2 write1538320 words to FDRI

这些指令的含义如下:

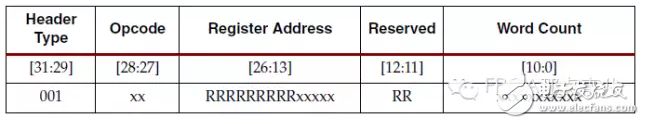

FPGA配置bit流包含两种类型的配置字指令,第一种类型为读写操作指令,格式如下

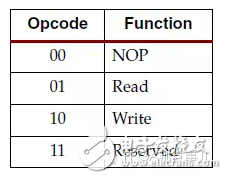

R为保留位,没有实际意义。其中Opcode的含义如下

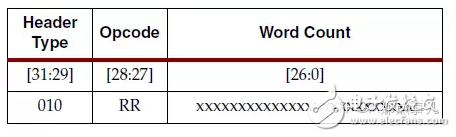

第二种类型的配置字指令必须跟随在类型一之后,用于长字节的写操作

一些状态寄存器的地址如下所示