首先,了解一下SWM190芯片的时钟频率特点。它的最大时钟频率可以达到60MHz,并提供五种时钟源供用户选择:

1. 内部高频振荡器(RCHF):这是一种片内时钟源,无需外部器件支持,频率为24MHz或48MHz,通过HRCCR寄存器切换,精度达到百分之一。 2. 内部低频振荡器(RCLF):同样为片内时钟源,无需外部连接,频率固定为32KHz。 3. 外部振荡器(XTAH):可连接4~32MHz的外部振荡器。 4. 外部低频振荡器(XTAL):支持32.768KHz的外部低频时钟输入。 5. PLL:可使用RCHF或XTAH作为输入源。

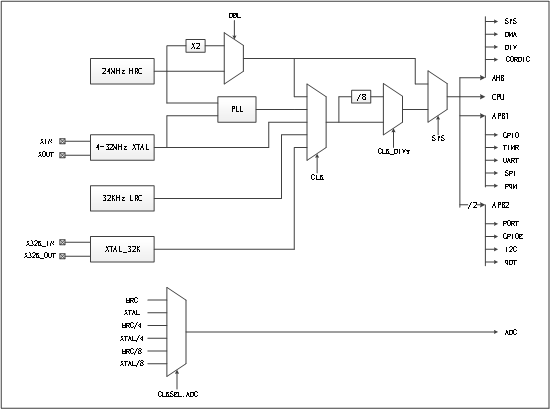

了解了时钟源后,我们来探讨时钟系统的框图。框图显示了SWM190芯片的时钟系统结构,帮助用户更好地理解时钟配置。

在SWM190固件库中,系统时钟频率的选择被大大简化。用户可以直接调用SystemInit(void)函数配置系统时钟,但在调用前需要设置一些宏定义,这些定义位于system_SWM190.c文件中。

以下是一些时钟频率的宏定义选项:

- SYS_CLK_24MHz:内部高频24MHz RC振荡器。 - SYS_CLK_3MHz:内部高频3MHz RC振荡器。 - SYS_CLK_48MHz:内部高频48MHz RC振荡器。 - SYS_CLK_6MHz:内部高频6MHz RC振荡器。 - SYS_CLK_XTAL:外部晶体振荡器(2-30MHz)。 - SYS_CLK_XTAL_DIV8:外部晶体振荡器(2-30MHz)8分频。 - SYS_CLK_PLL:锁相环输出。 - SYS_CLK_PLL_DIV8:锁相环输出8分频。 - SYS_CLK_32KHz:内部低频32KHz RC振荡器。 - SYS_CLK_XTAL_32K:外部低频32KHz晶体振荡器。

用户只需修改SYS_CLK宏定义,即可改变系统时钟。

接下来,我们来看一下PLL的设定。PLL的输入参考时钟源可以是内部高频时钟或外部高频晶振输入,最大输出时钟频率为60MHz。配置PLL时,需要设置几个寄存器,公式为:VCO输出频率=PLL输入时钟/INDIV*4*FBDIV,PLL输出频率=VCO输出频率/OUTDIV。

具体宏定义如下:

- SYS_PLL_SR:可取值SYS_CLK_24MHz、SYS_CLK_48MHz、SYS_CLK_XTAL。 - PLL_IN_DIV:根据SYS_PLL_SRC的值设定,如SYS_PLL_SRC=SYS_CLK_24MHz时使用6。 - PLL_FB_DIV:设定值。 - PLL_OUT_DIV:可选值包括PLL_OUT_DIV8、PLL_OUT_DIV4、PLL_OUT_DIV2。

在system_SWM190.c文件中,还提供了运行过程中更改时钟的函数,如SystemCoreClockUpdate()、SwitchTo24MHz()、switchTo3MHz()等,方便用户在系统运行过程中修改系统时钟。

通过上述介绍,我们可以看到SWM190芯片在系统时钟配置方面的灵活性和便利性。这不仅提高了设计的灵活性,还让用户可以根据实际需求轻松调整系统时钟,从而优化性能和功耗。

系统时钟

华芯微特科技有限公司SWM系列芯片可通过软件配置改变时钟的速度,可以让我们的设计更加灵活,频率可选空间也更加广泛,用户可以根据自己的实际需求配置需要的系统时钟。为了让用户能够更简单的使用这一功能,下面小编将以SWM190为例,给大家展示如何配置SWM系列产品的系统时钟。

SWM190最大时钟频率可达 60MHz

有5个时钟源可供使用:

01、内部高频振荡器(RCHF):内部高频振荡器为片内时钟源,无需连接任何外部器件。频率为24MHz或48MHz,通过HRCCR寄存器进行切换,精度为百分之一,可提供较精确的固定频率时钟.

02、内部低频振荡器(RCLF):内部低频振荡器为片内时钟源,无需连接任何外部器件。频率为32KHz。

03、外部振荡器(XTAH):外部振荡器可接4~32MHz频率.

04、外部低频振荡器(XTAL):外部低频振荡器,支持32.768KHz时钟接入

05、PLL:支持RCHF或XTAH作为输入源

我们来看一下时钟系统框图

如图所示:

SWM190时钟框图

SWM190时钟框图

SWM190时钟配置方法

在SWM190固件库中对时钟频率的选择进行了简化,原先的很多操作都在后台进行。系统给出的函数为SystemInit(void),可直接调用配置系统时钟,但在调用前还需要进行一些宏定义的设置,具体的设置在system_SWM190.c文件中。

如下:

/* 系统时钟设定 */

#define SYS_CLK_24MHz 0 //0 内部高频24MHz RC振荡器 #define SYS_CLK_3MHz 1 //1 内部高频 3MHz RC振荡器 #define SYS_CLK_48MHz 2 //2 内部高频48MHz RC振荡器 #define SYS_CLK_6MHz 3 //3 内部高频 6MHz RC振荡器 #define SYS_CLK_XTAL 4 //4 外部晶体振荡器(2-30MHz) #define SYS_CLK_XTAL_DIV8 5 //5 外部晶体振荡器(2-30MHz) 8分频 #define SYS_CLK_PLL 6 //6 锁相环输出 #define SYS_CLK_PLL_DIV8 7 //7 锁相环输出 8分频 #define SYS_CLK_32KHz 8 //8 内部低频32KHz RC 振荡器 #define SYS_CLK_XTAL_32K 9 //9 外部低频32KHz 晶体振荡器 #define SYS_CLK SYS_CLK_48MHz

//您只需要修改此处SYSCLK宏定义来修改系统时钟。

SWM190PLL 设定

PLL的输入参考时钟源可设置为内部高频时钟或外部高频晶振输入,最大输出时钟可设置为60MHz。

当系统时钟配置为PLL时钟时,可通过配置以下几处寄存器来配置PLL时钟,其配置公式为:VCO输出频率=PLL输入时钟/INDIV*4*FBDIV

PLL输出频率=PLL输入时钟/INDIV*4*FBDIV/OUTDIV=VCO输出频率/OUTDIV

具体宏定义如下:

#define SYS_PLL_SR SYS_CLK_24MHz //可取值SYS_CLK_24MHz、SYS_CLK_48MHz、SYS_CLK_XTAL #define PLL_IN_DIV 6 //SYS_PLL_SRC = SYS_CLK_24MHz 时用6,SYS_PLL_SRC= SYS_CLK_48MHz 时用 12 #define PLL_FB_DIV 30 #define PLL_OUT_DIV8 0 #define PLL_OUT_DIV4 1 #define PLL_OUT_DIV2 2 #define PLL_OUT_DIV PLL_OUT_DIV8

//此外,在system_SWM190.c文件中还定义了运行过程中更改时钟函数

SystemCoreClockUpdate()

switchTo24MHz()

switchTo3MHz()

switchTo48MHz()

switchTo6MHz()

switchToXTAL()

switchToPLL()

switchTo32KHz()

switchToXTAL_32K()

等一系列的函数方便用户在系统运行过程中修改系统时钟时使用。

审核编辑:彭菁