首先,我们需要定义一个配置对象。这个对象将包含DUT的所有可配置参数,方便我们在测试过程中进行管理。以下是一个简单的配置对象定义示例:

```verilog class dut_config extends uvm_object; `uvm_object_utils(dut_config) // 定义配置参数 int unsigned param1; bit [31:0] param2; function new(string name = "dut_config"); super.new(name); endfunction endclass ```

接下来,在UVM测试中,我们要创建并设置这个配置对象,然后通过UVM配置数据库进行传递。以下是一个创建和设置配置对象的示例:

```verilog class my_test extends uvm_test; `uvm_component_utils(my_test) dut_config cfg; function new(string name = "my_test", uvm_component parent = null); super.new(name, parent); endfunction virtual function void build_phase(uvm_phase phase); super.build_phase(phase); // 创建并配置DUT配置对象 cfg = dut_config::create("cfg"); cfg.param1 = 10; cfg.param2 = 'hDEADBEEF; // 将DUT配置对象设置到UVM配置数据库 if (!uvm_config_db #(dut_config)::set(this, "*", "cfg", cfg)) begin `uvm_fatal("SETCFG", "Unable to set DUT configuration in the UVM configuration DB") end endfunction endclass ```

在UVM参考模型中,我们可以从UVM配置数据库中获取这个配置对象。以下是如何在参考模型中获取配置对象的示例:

```verilog class ref_model extends uvm_component; `uvm_component_utils(ref_model) dut_config cfg; function new(string name = "ref_model", uvm_component parent = null); super.new(name, parent); endfunction virtual function void build_phase(uvm_phase phase); super.build_phase(phase); // 从UVM配置数据库获取DUT配置对象 if (!uvm_config_db #(dut_config)::get(this, "", "cfg", cfg)) begin `uvm_fatal("GETCFG", "Unable to get DUT configuration from the UVM configuration DB") end endfunction endclass ```

以上步骤展示了如何通过UVM配置数据库传递DUT配置信息给UVM参考模型。根据具体的设计和验证需求,这个过程可能需要进行相应的调整。

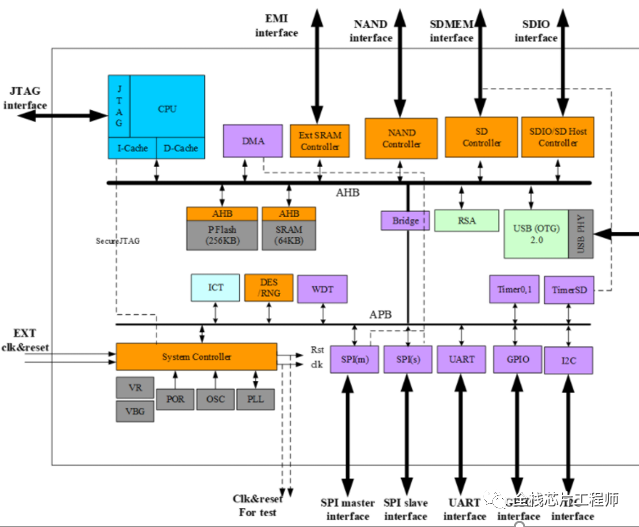

在实际的项目中,例如MCU+ISP图像处理芯片的设计,这种方法尤为重要。项目启动时,我们可以利用UVM的方法论,将设计、验证、DFT和后端的知识点罗列出来,与团队成员一起讨论和完善。

通过项目驱动的教学方法,我们可以介绍MCU芯片全流程设计的方法,提炼相关的检查列表和signoff checklist样本,帮助团队成员熟悉SoC架构、设计流程、开发进度和项目管理。这种方式不仅提高了设计效率,还确保了项目质量。

编辑:黄飞

在基于Universal Verification Methodology (UVM) 的设计中,将配置从设计被测设备 (DUT) 传递到UVM参考模型通常涉及以下步骤:

定义一个配置对象:首先,需要定义一个包含DUT配置的UVM配置对象。这个对象通常会包含被测设备的所有可配置参数。

class dut_config extends uvm_object; `uvm_object_utils(dut_config) // Define your configuration parameters here. For example: int unsigned param1; bit [31:0] param2; function new(string name = "dut_config"); super.new(name); endfunction endclass

在测试中创建和设置配置对象:在UVM测试 (UVM test) 中,创建并设置此配置对象,然后通过UVM配置数据库 (UVM config DB) 设置。

class my_test extends uvm_test; `uvm_component_utils(my_test) dut_config cfg; function new(string name = "my_test", uvm_component parent = null); super.new(name, parent); endfunction virtual function void build_phase(uvm_phase phase); super.build_phase(phase); // Create and configure the DUT configuration object cfg = dut_config::create("cfg"); cfg.param1 = 10; cfg.param2 = 'hDEADBEEF; // Set the DUT configuration object in the UVM configuration DB if (!uvm_config_db #(dut_config)::set(this, "*", "cfg", cfg)) begin `uvm_fatal("SETCFG", "Unable to set DUT configuration in the UVM configuration DB") end endfunction endclass

在UVM参考模型中获取配置对象:在UVM参考模型中,可以从UVM配置数据库中获取此配置对象。

class ref_model extends uvm_component; `uvm_component_utils(ref_model) dut_config cfg; function new(string name = "ref_model", uvm_component parent = null); super.new(name, parent); endfunction virtual function void build_phase(uvm_phase phase); super.build_phase(phase); // Get the DUT configuration object from the UVM configuration DB if (!uvm_config_db #(dut_config)::get(this, "", "cfg", cfg)) begin `uvm_fatal("GETCFG", "Unable to get DUT configuration from the UVM configuration DB") end endfunction endclass

以上示例展示了一种常见的通过UVM配置数据库将DUT的配置传递给UVM参考模型的方法。具体的实现可能会根据设计和验证需求进行调整。

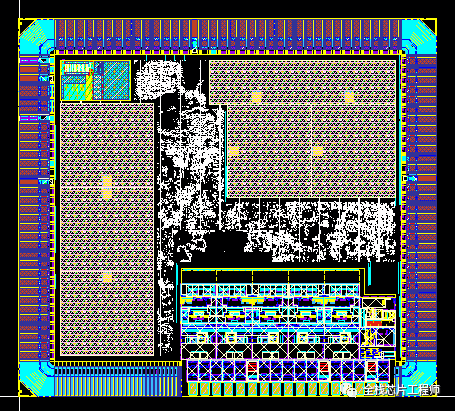

实战MCU+ISP图像处理芯片版图

知识星球发起MCU项目启动,大家一起参与MCU项目规格启动讨论,我把设计、验证、DFT、后端的知识点全部罗列出来,大家一起来完善。

以项目驱动的方式介绍MCU芯片全流程设计的方法;提炼相关的检查列表、signoff checklist的样本;让星球成员熟悉SoC架构、设计流程、开发进度、项目管理;

编辑:黄飞